# GDL and trigger data readout TRG/DAQWS@BINP

TRG/DAQWS@BINP 20160906 H. Nakazawa

## GDL (Global Decision Logic)

#### **\*** Implemented on UT3 in Ehut, accessible with vmetrg18

## ut bits from subtrigger 1

|     | nbits | name       |                       |  |  |

|-----|-------|------------|-----------------------|--|--|

|     | 3     | n_t3_full  | #of 3D full tracks    |  |  |

|     | 3     | n_t3_short | #of 3D short tracks   |  |  |

|     | 3     | n_t2_full  | #of 2D full tracks    |  |  |

| CDC | 3     | n_t2_shoft | #of 2D short tracks   |  |  |

|     | 1     | cdc_bb     | back-to-back topology |  |  |

|     | 1     | cdc_open45 | 45 deg opening angle  |  |  |

|     | 3     | cdc_timing | timing signal         |  |  |

|     | 1     | e_high     | 1 GeV or more         |  |  |

|     | 1     | e_low      | 0.5 GeV or more       |  |  |

|     | 1     | e_lum      | 3 GeV or more         |  |  |

| ECL | 1     | ecl_bha    | Bhabha                |  |  |

|     | 11    | bha_type   | Identified as Bhabha  |  |  |

|     | 4     | n_clus     | # of cluster          |  |  |

|     | 1     | ecl_timing | timing signal         |  |  |

nkzw

## ut bits from subtrigger 1

|        | nbits | name         |                       |  |  |

|--------|-------|--------------|-----------------------|--|--|

|        | 3     | n_hits       | # of top hits         |  |  |

| TOD    | 1     | top_bb       | back-to-back topology |  |  |

| TOP    | 1     | top_active   | Top Timing active     |  |  |

|        | 3     | top_timing   | Top Timing            |  |  |

| KLM    | 3     | n_klm        | # of klm hits         |  |  |

| Random | 1     | revo         |                       |  |  |

|        | 2     | rand         |                       |  |  |

|        | 3     | bhabha_delay |                       |  |  |

nkzw

## Logic (FTDL and PSNM bits)

#### v0.02

|                                | PS | Logic = algorithm                                      |  |  |  |  |

|--------------------------------|----|--------------------------------------------------------|--|--|--|--|

| 3 3D tracks                    | 1  | zzx = (n_t3_full >= 2) & (n_t3_short >= 3)             |  |  |  |  |

| 3 2D tracks                    | 1  | ffs = $(n_t2_fu \parallel >= 2) \& (n_t2_short >= 3)$  |  |  |  |  |

| 1 GeV or more                  | 1  | hie = e_high & (! bhabha)                              |  |  |  |  |

| 4 clusters                     | 1  | c4 = n_clus >= 4                                       |  |  |  |  |

|                                | 1  | zx = (n_t3_full >= 1) & (n_t3_short >= 2) & (! bhabha) |  |  |  |  |

| LowMult                        | 1  | fs = (n_t2_full >= 1) & (n_t2_short >= 2) & (! bhabha) |  |  |  |  |

| Bhabha                         | 50 | bha = bhabha                                           |  |  |  |  |

| Бпарпа                         | 50 | bhatrk = e_lum & (n_t2_short == 2)                     |  |  |  |  |

| ee $\rightarrow \gamma \gamma$ | 10 | gg = bhabha & (n_t2_short == 0)                        |  |  |  |  |

| mu pair                        | 1  | mupair = (n_t2_short == 2) & (n_klm == 2)              |  |  |  |  |

|                                | 1  | revolution = revo                                      |  |  |  |  |

| random                         | 1  | random = rand                                          |  |  |  |  |

|                                | 1  | bg = bhabha_delay                                      |  |  |  |  |

PS = prescale FTDL = Final Trigger Decision Logic PSNM = FTDL after prescale

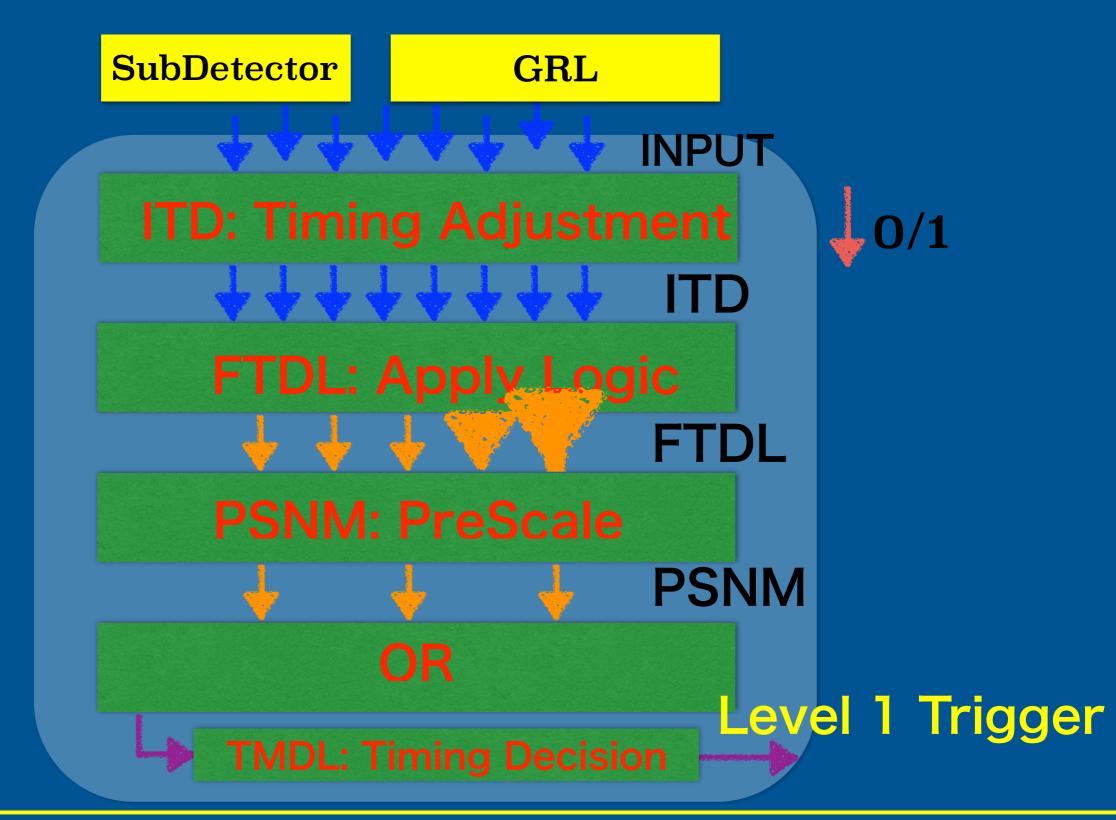

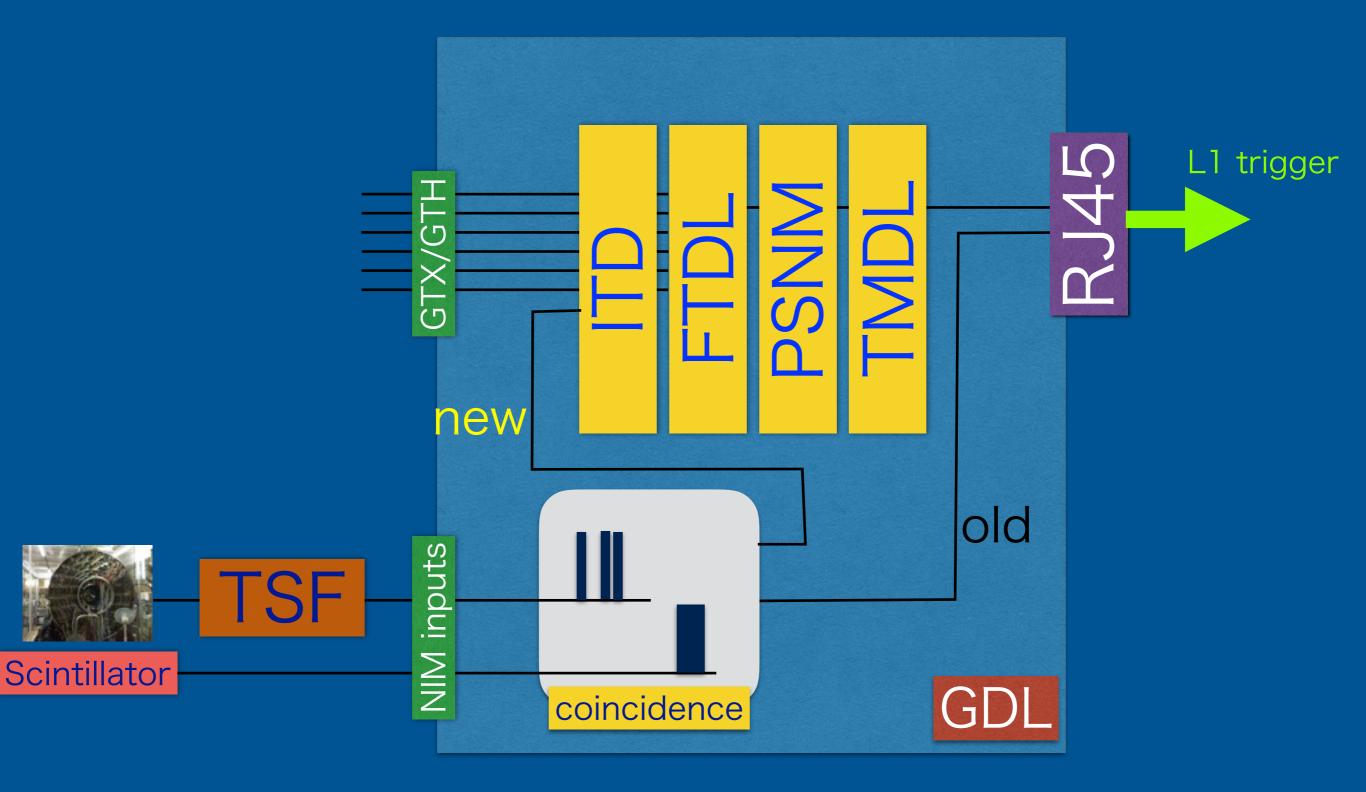

# **GDL Firmware updates**

#### ✓ ITD

- ✓ Function to extend input signal length added

- ✓ Needed to take coincidence in FTD

- ✓ GDL receives rising edge timing only

- ✓ Different valid signal widths for each input

- $\checkmark$  Controlled via VME

- ✓ TMDL

- $\checkmark$  BUSY signal length changeable via VME

- ✓ 200 nsec requirement by DAQ

- $\checkmark$  ~500 nsec maximum variation of TSF signal

# **CDC Cosmic Ray Test**

nkzw

# **GDL Monitor**

| •                                      |                                                     |                      | trgadmin@vmetrg18:~/                                                    | n — ssh -XY          | odaq.local.ke                | ek.jp — 1 | 51×18                                      |                |                           |             |  |

|----------------------------------------|-----------------------------------------------------|----------------------|-------------------------------------------------------------------------|----------------------|------------------------------|-----------|--------------------------------------------|----------------|---------------------------|-------------|--|

|                                        | trgadmin@vmetrg18:~/n — ssh -XY bdaq.local.kek.jp + |                      |                                                                         |                      |                              |           |                                            | +              |                           |             |  |

| Clock                                  | counter: 0x00002749-a219cbd4,                       | running abou         | ut 3 day 22 hrs 28 mi                                                   | 1 55 sec             |                              |           |                                            |                |                           |             |  |

| 0 zzx                                  |                                                     |                      | 6 bhabha                                                                | 0,                   | 0,                           |           | 12 bg                                      | 0,             | 0,                        | 0           |  |

| 1 ffs<br>2 zx<br>3 fs<br>4 hie<br>5 c4 | 0, 0,<br>0, 0,                                      | 3, 0<br>3, 0<br>3, 0 | 7 bhabha_trk<br>  8 gg<br>  9 mu_pair<br>  10 revolution<br>  11 random | 0,<br>0,<br>0,<br>0, | 0,<br>0,<br>0,<br>110,<br>0, | 0         | 13 nim0<br>14 nim1<br>15 nim2<br>16 crtout | 0,<br>0,<br>1, | 0,<br>0,<br>0,<br>970318, | 0<br>0<br>0 |  |

|                                        |                                                     |                      |                                                                         |                      |                              |           | PSNM                                       | 1              |                           |             |  |

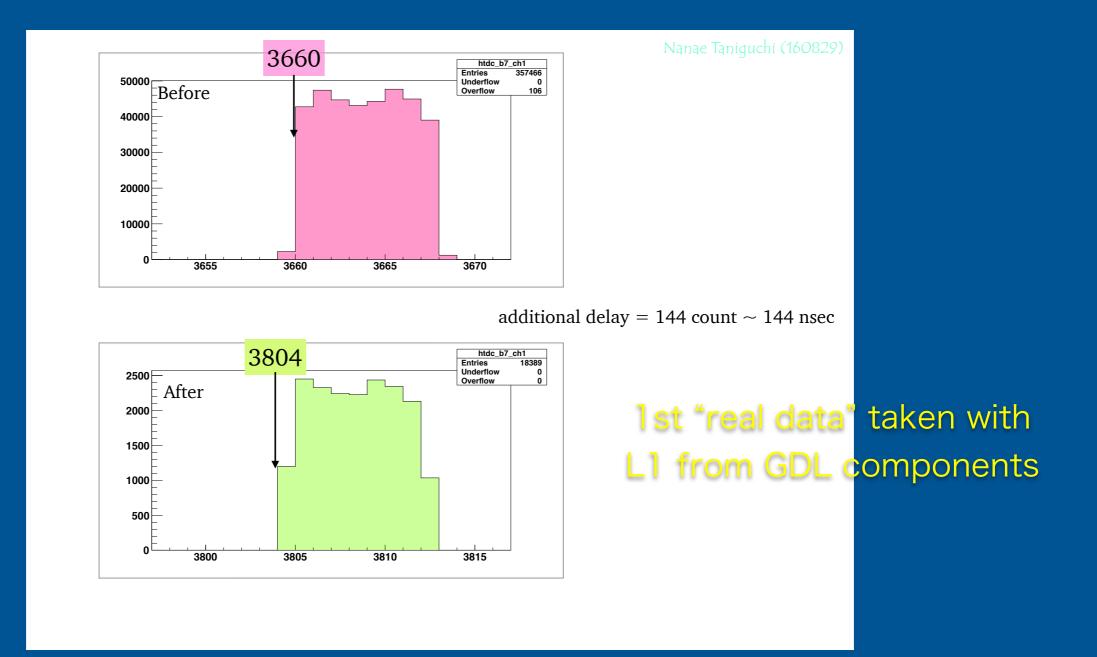

## **CDC CRT; GDL Latency**

- ✓ 96 nsec for TMDL time window

- Study needed to select proper time window length

nkzw

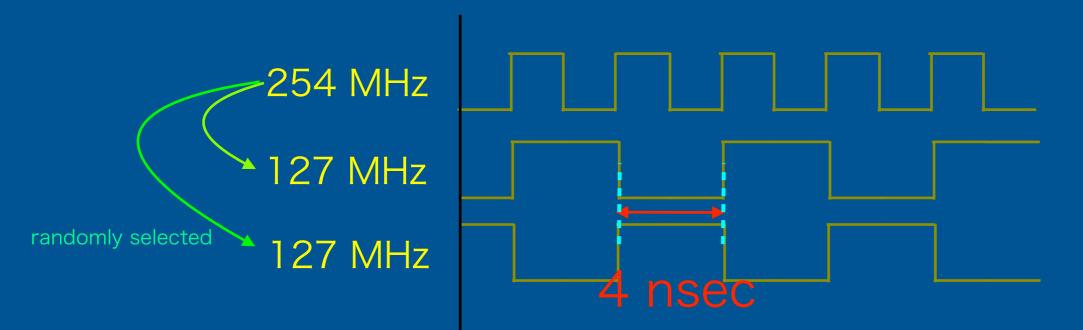

#### CDC CRT; Timing Shift Problem Y. Iwasaki/N. Taniguchi

- ✓ 4 nsec timing shift observed after rebooting crate

- ✓ 127 MHz was generated using 254 MHz

- ✓ 254 MHz for GTH

- Two 127-MHz clocks with different phase generated randomly

- (Seems to be) solved by changing clock source

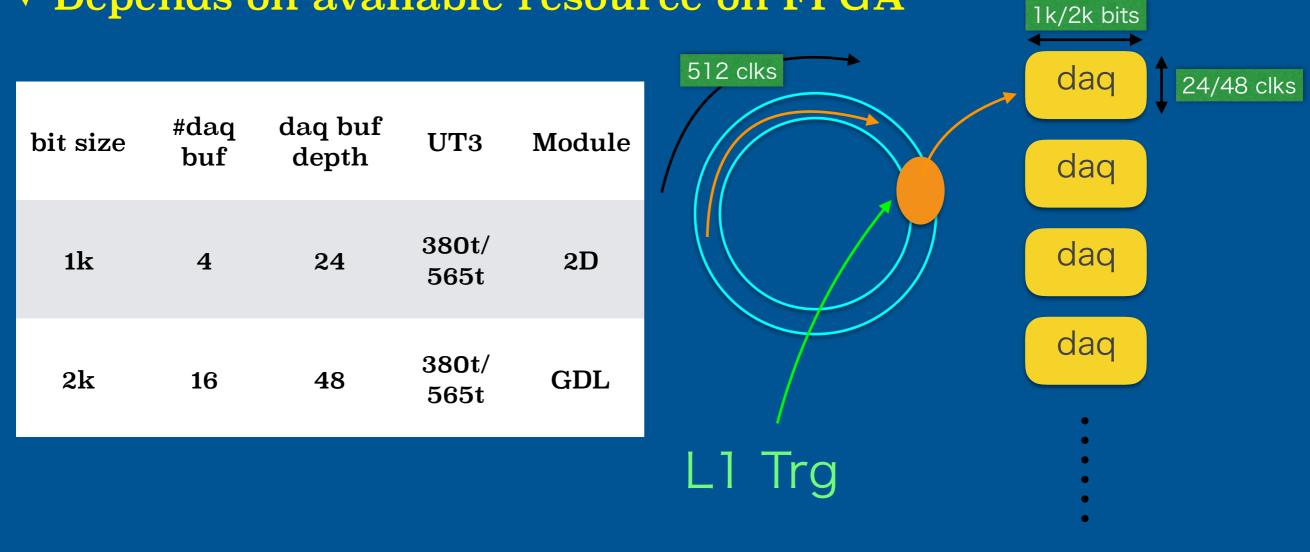

### **Event Buffer for b2l on UT3**

#### ✓ Hyunki's version

- ✓ Modified for different configurations (bit size, number of DAQ buffer, BRAM depth, address size, data clock, 380t/565t)

- ✓ Depends on available resource on FPGA

#### 2D(CDCTRG) data taking through b2l

- ✓ For debugging 2D Firmware

- ✓ Merger play mode; Simulation data given to Merger

- $\checkmark$  Merger -> TSF -> 2D

- ✓ Event buffer

- ✓ outputs have 8 clock width

- ✓ 1k bit, 4 DAQ buffer, 24 clock depth

- ✓ Dedicated trigger using TSF

- ✓ GDL -> FTSW228 -> 2D

- ✓ Delay for this cycle adjustable through VME

- $\checkmark$  Dummy data test ok, will under go this week.

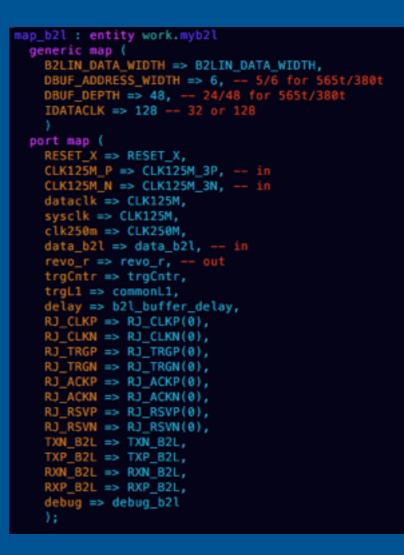

### **b2l + b2tt unified interface**

- ✓ b2l + b2tt + Event buffer

- ✓ To clean up top.vhd

- Signals to connect b2tt and b2l hidden

- ✓ To increase b2l easily if necessary

- Without increasing Event buffer size

- UT3 has 40 GTX lanes (4 RJ45)

- Any reason to have separate component?

# GDL data

- ✓ 96 inputs (input, inputDelayed)

- ✓ 192 outputs (ftd, psnm)

- ✓ TMDL outputs

- $\checkmark$  timing source 3 bit +  $\alpha$

- ✓ Raw mode

- Record everything within time window

- ✓ Except for "inputs" due to large timing variation ~ 2usec

- $\checkmark$  476 +  $\alpha$  bits, 48 clocks ~ 3 kB/event

- ✓ Suppress mode

- ✓ bit number + rising timing for only fired bit in 32bit word

- ✓ 100 fired \* 32bit < 0.5 kB/event

# **Trigger Data**

|        |     | #UT3 | B/ev   | MB/sec   |                 |

|--------|-----|------|--------|----------|-----------------|

| GDL    |     | 1    | 500    | 15       |                 |

| GRL    |     | 1    |        |          |                 |

| ECLTRG |     | 1    | 400    | 11       |                 |

| KLMTRG |     | 1    | 7/muon | 0.2/muon | Sent to GRL     |

| TOPTRG |     | 2    |        |          | No b2I? To GRL? |

| CDC    | TSF | 9    |        |          |                 |

| CDC    | 2D  | 4    |        |          |                 |

| CDC    | 3D  | 4    |        |          |                 |

| CDC    | NN  | 4    |        |          |                 |

| CDC    | ETF | 1    |        |          | No b2l?         |

| Total  |     |      |        |          |                 |

#### ✓ GDL is ready to debug using real data.